本(běn)文(wén)是基于(yú)USRP-4120平台,对(duì)AD9361主(zhǔ)要(yào)特(tè)性(xìng)的(de)闡述,由(yóu)此(cǐ)引申出設計(jì)时(shí)需要(yào)注意(yì)的(de)细节(jié)。

3 本(běn)振性(xìng)能(néng)

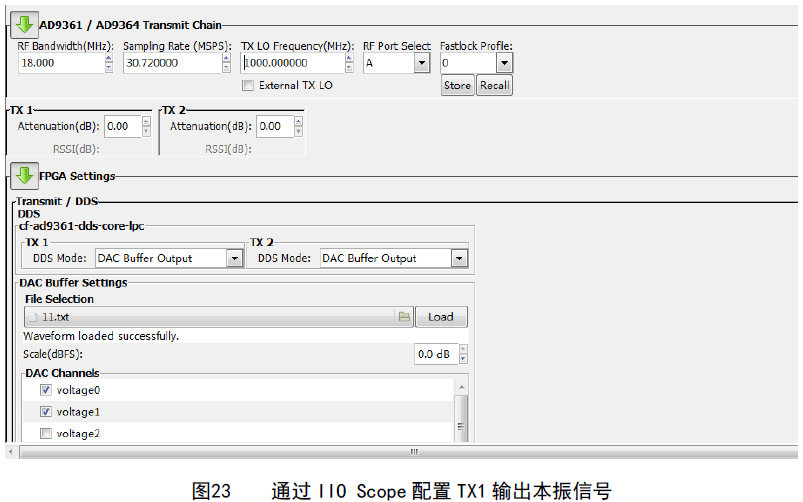

按照下(xià)图(tú)配置IIO Scope參數,使TX1通(tòng)道(dào)輸出本(běn)振信号(hào)。

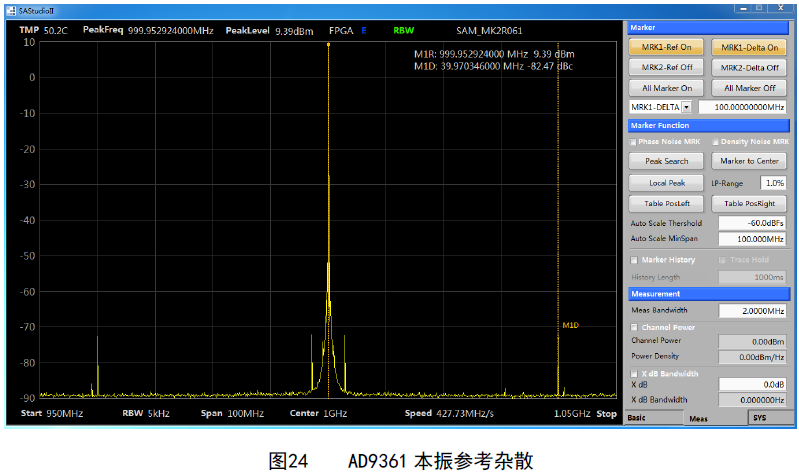

3.1 參考雜散(sàn)

頻譜儀上(shàng)顯示輸出本(běn)振頻譜,其中包(bāo)含LO±40MHz雜散(sàn),这(zhè)是參考雜散(sàn),40MHz參考信号(hào)調制到(dào)本(běn)振信号(hào)上(shàng)形成(chéng)的(de)雜散(sàn)。

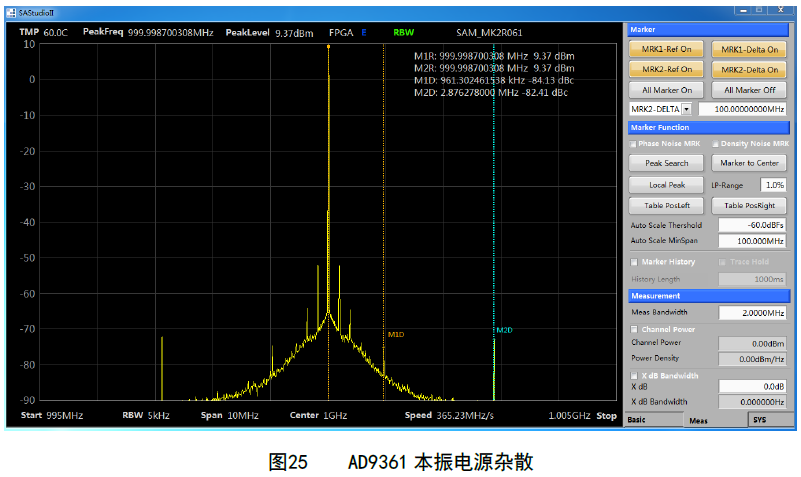

3.2 電(diàn)源雜散(sàn)

Span調整为(wèi)10MHz,頻譜如(rú)下(xià)所(suǒ)示,可(kě)以(yǐ)發(fà)現(xiàn)有(yǒu)961kHz和(hé)2.876MHz的(de)調制雜散(sàn),这(zhè)是電(diàn)源雜散(sàn),来(lái)源于(yú)DC-DC電(diàn)源的(de)開(kāi)關(guān)頻率,通(tòng)常需要(yào)依靠電(diàn)源旁路(lù)電(diàn)容和(hé)LDO来(lái)抑制,本(běn)測試平台硬(yìng)件(jiàn)使用(yòng)的(de)DC-DC为(wèi)LTM4644,開(kāi)關(guān)頻率为(wèi)1MHz,與(yǔ)該雜散(sàn)相近(jìn)。

4.3 PLL雜散(sàn)

4.3.1 現(xiàn)象(xiàng)

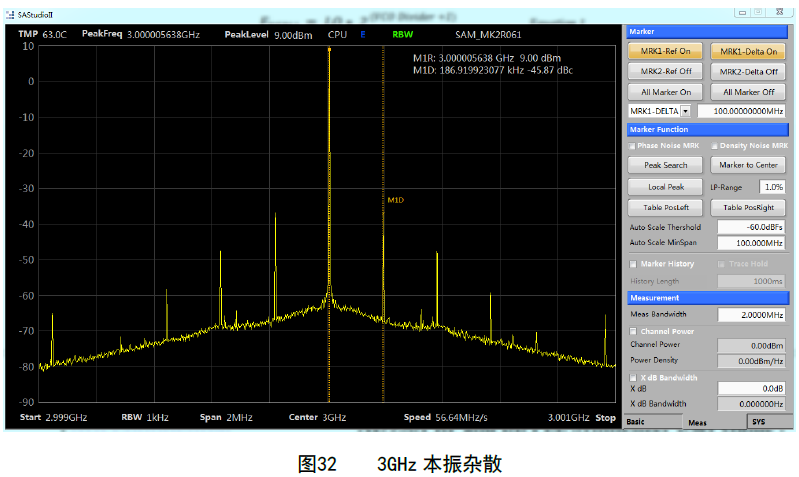

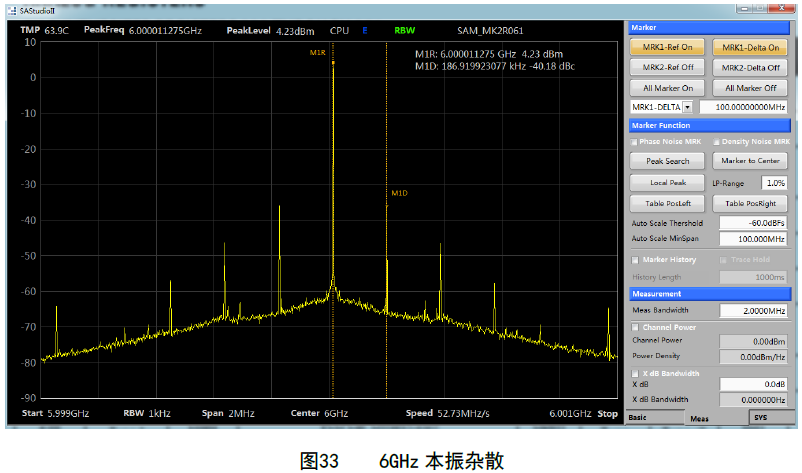

上(shàng)文(wén)提(tí)到(dào)PLL雜散(sàn)出現(xiàn)在(zài) (N、k为(wèi)整數)頻點(diǎn)下(xià),主(zhǔ)要(yào)表(biǎo)現(xiàn)为(wèi)約187kHz的(de)調制雜散(sàn),如(rú)下(xià)图(tú)所(suǒ)示。

3.3.2 PLL原理(lǐ)簡介

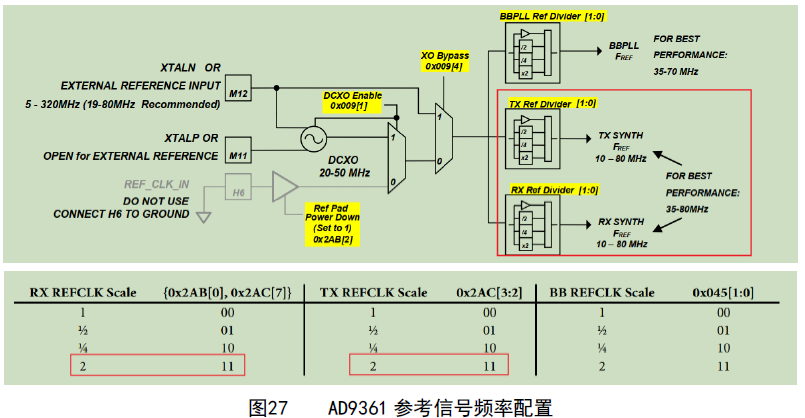

9361的(de)輸入(rù)參考时(shí)鐘(zhōng)頻率Clk为(wèi)40MHz,經(jīng)过(guò)TX/RX Ref Divider分(fēn)頻、旁路(lù)或(huò)倍頻,産生RF PLL所(suǒ)需的(de)參考。

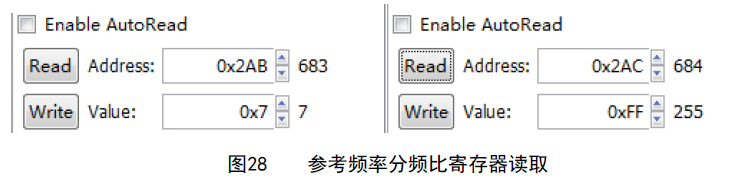

TX Ref Divider和(hé)TX Ref Divider的(de)配置寄存器为(wèi)0x2AB、0x2AC:

读(dú)取(qǔ)寄存器的(de)值,0x2AB的(de)值为(wèi)0x7,0x2AC的(de)值为(wèi)0xFF,TX Ref Divider和(hé)TX Ref Divider对(duì)輸入(rù)參考進(jìn)行了(le)2倍頻,RF PLL的(de)輸入(rù)參考为(wèi)80MHz。即Fref = 2*Clk。

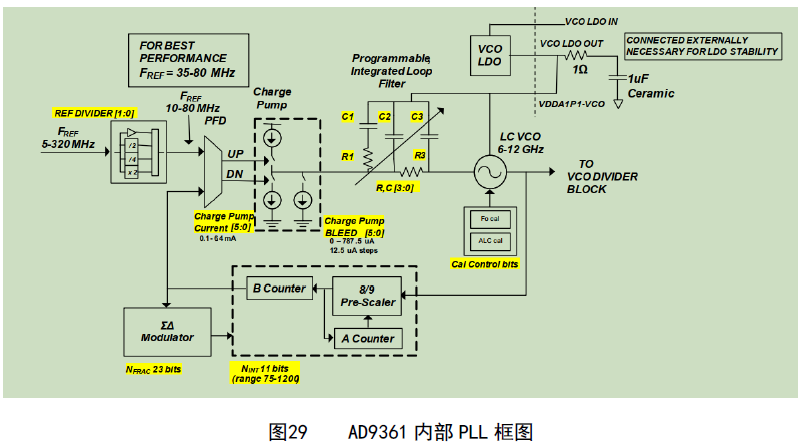

80MHz的(de)參考頻率(Fref)輸入(rù)到(dào)PLL后,産生6~12GHz的(de)VCO,如(rú)下(xià)图(tú)所(suǒ)示。

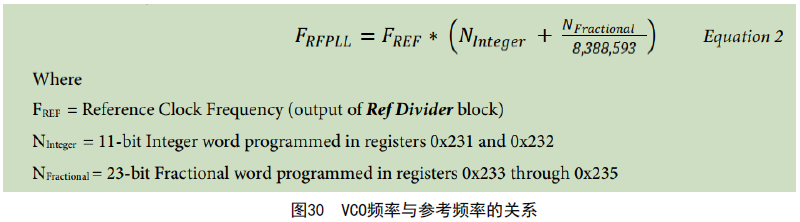

FVCO頻率與(yǔ)Fref的(de)關(guān)系(xì)如(rú)下(xià)图(tú)所(suǒ)示:

上(shàng)图(tú)可(kě)以(yǐ)看(kàn)出,RF PLL是一(yī)个(gè)小數分(fēn)頻鎖相环(huán),可(kě)以(yǐ)将VCO頻率與(yǔ)Fref的(de)關(guān)系(xì)簡易为(wèi)FVCO = Fref*N,其中N可(kě)以(yǐ)是整數,也(yě)可(kě)以(yǐ)是小數。

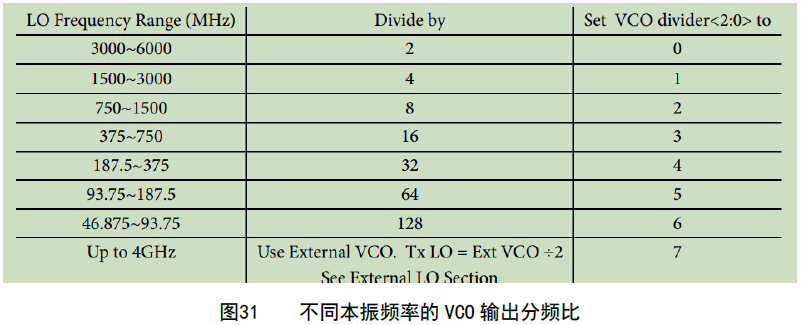

VCO頻率範圍为(wèi)6~12GHz,需要(yào)分(fēn)頻才能(néng)産生所(suǒ)需的(de)LO信号(hào),根(gēn)據(jù)所(suǒ)需的(de)頻率,分(fēn)頻比按照下(xià)图(tú)配置。

分(fēn)頻系(xì)數为(wèi)k,本(běn)振頻率FLO = FVCO/2k。

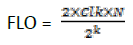

所(suǒ)以(yǐ)LO與(yǔ)9361輸入(rù)时(shí)鐘(zhōng)的(de)關(guān)系(xì)可(kě)以(yǐ)表(biǎo)示为(wèi):

其中: FLO为(wèi)本(běn)振頻率;Clk为(wèi)9361輸入(rù)时(shí)鐘(zhōng),頻率为(wèi)40MHz;N为(wèi)PLL的(de)分(fēn)頻比,可(kě)以(yǐ)取(qǔ)整數或(huò)小數;k为(wèi)VCO輸出分(fēn)頻系(xì)數。

3.3.3 測試过(guò)程

Clk整數倍頻點(diǎn)測試

測試Clk頻率的(de)整數倍頻點(diǎn),即LO=M*Clk(M为(wèi)整數),發(fà)現(xiàn)都存在(zài)187kHz雜散(sàn),下(xià)图(tú)为(wèi)3GHz、6GHz示例。

Clk/2的(de)整數倍頻點(diǎn)測試

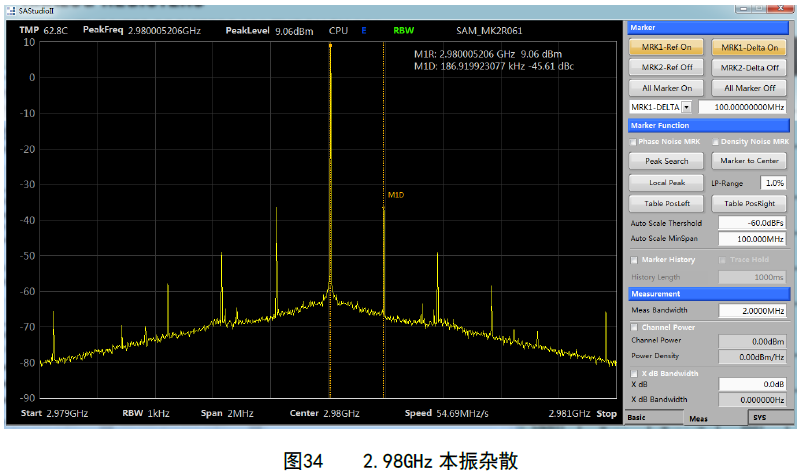

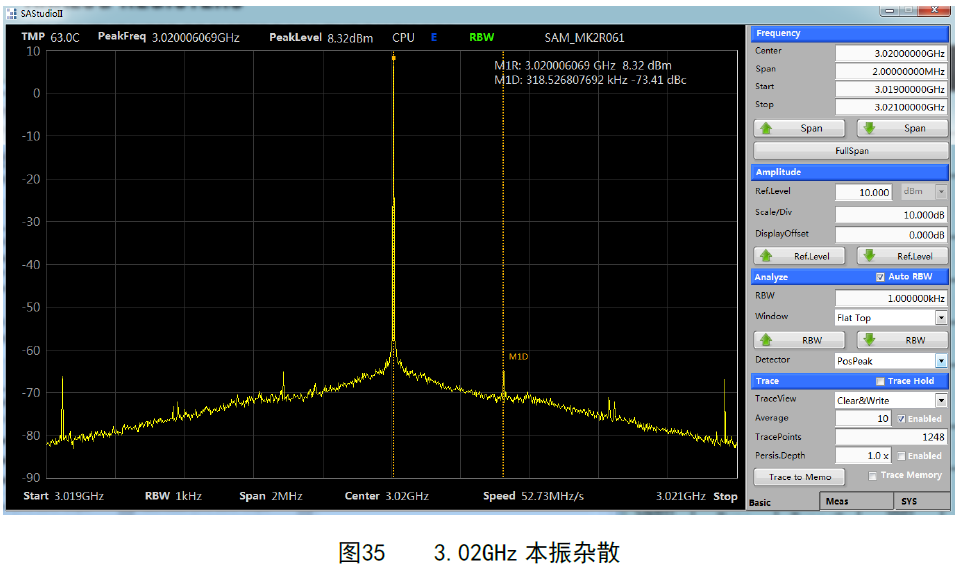

測試Clk/2的(de)整數倍頻點(diǎn)(不(bù)含Clk整數倍頻點(diǎn)),即LO=M*Clk/2(M为(wèi)奇數),發(fà)現(xiàn)2.98GHz存在(zài)187kHz雜散(sàn),但3,02GHz不(bù)含該雜散(sàn)。

上(shàng)图(tú)为(wèi)2.98GHz的(de)輸出頻譜,VCO輸出分(fēn)頻系(xì)數k为(wèi)2,按照 ![]() 公(gōng)式計(jì)算N=149。

公(gōng)式計(jì)算N=149。

上(shàng)图(tú)为(wèi)3.02GHz的(de)輸出頻譜,VCO輸出分(fēn)頻系(xì)數k为(wèi)1,按照![]() 公(gōng)式計(jì)算N=75.5。

公(gōng)式計(jì)算N=75.5。

Clk/2n的(de)整數倍頻點(diǎn)測試

測試Clk/4、Clk/8…等的(de)整數倍頻點(diǎn),会(huì)發(fà)現(xiàn)在(zài)某个(gè)頻率處(chù),低(dī)于(yú)此(cǐ)頻率的(de)頻點(diǎn)会(huì)有(yǒu)187kHz雜散(sàn),高(gāo)于(yú)此(cǐ)頻率的(de)頻點(diǎn)無187kHz雜散(sàn),如(rú)下(xià)表(biǎo)所(suǒ)示。

| 有(yǒu)PLL雜散(sàn)的(de)最(zuì)高(gāo)頻點(diǎn)F1/MHz | F1下(xià)的(de)分(fēn)頻比N | 無PLL雜散(sàn)的(de)最(zuì)低(dī)頻點(diǎn)F2/MHz | F2下(xià)的(de)分(fēn)頻比N | |

| Clk/4整數倍頻點(diǎn) | 1490 | 149 | 1510 | 75.5 |

| Clk/8整數倍頻點(diǎn) | 745 | 149 | 755 | 75.5 |

| Clk/16整數倍頻點(diǎn) | 372.5 | 149 | 377.5 | 75.5 |

| Clk/32整數倍頻點(diǎn) | 186.25 | 149 | 188.75 | 75.5 |

| Clk/64整數倍頻點(diǎn) | 93.125 | 149 | 94.375 | 75.5 |

結論

根(gēn)據(jù)以(yǐ)上(shàng)測試,發(fà)現(xiàn)187kHz雜散(sàn)出現(xiàn)在(zài)PLL分(fēn)頻比为(wèi)整數的(de)条(tiáo)件(jiàn)下(xià)。當这(zhè)種(zhǒng)条(tiáo)件(jiàn)發(fà)生时(shí),小數分(fēn)頻需要(yào)配置为(wèi)0。