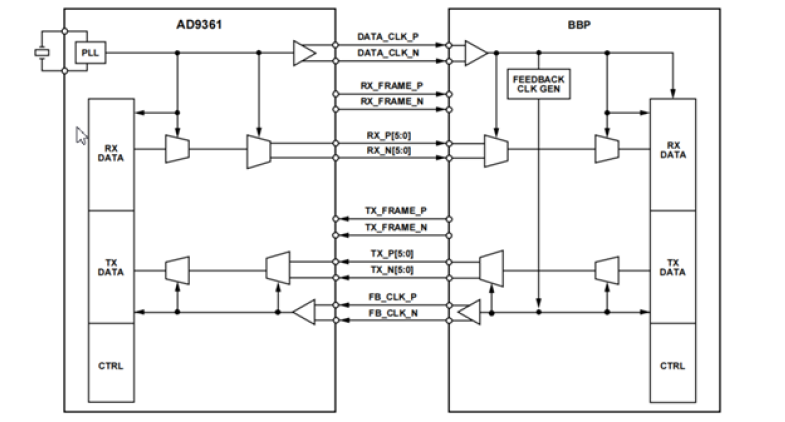

1、AD9361 LVDS模式下(xià)數據(jù)接收(shōu)簡介

AD9361 LVDS模式下(xià)數據(jù)收(shōu)發(fà)信号(hào)連(lián)接如(rú)下(xià)所(suǒ)示,对(duì)于(yú)數據(jù)接收(shōu),需要(yào)三(sān)種(zhǒng)信号(hào),DATA_CLK、RX_FRAME和(hé)RX_D[5:0],分(fēn)别对(duì)應(yìng)采樣(yàng)时(shí)鐘(zhōng)、接收(shōu)有(yǒu)效信号(hào)和(hé)數據(jù),这(zhè)三(sān)種(zhǒng)信号(hào)都是由(yóu)AD9361提(tí)供。BBP根(gēn)據(jù)有(yǒu)效信号(hào)和(hé)采樣(yàng)时(shí)鐘(zhōng)对(duì)數據(jù)總(zǒng)線(xiàn)的(de)信号(hào)進(jìn)行采樣(yàng)。在(zài)LVDS模式下(xià),采樣(yàng)时(shí)鐘(zhōng)必須为(wèi)DDR模式。

2 、毛(máo)刺問(wèn)題(tí)現(xiàn)象(xiàng)

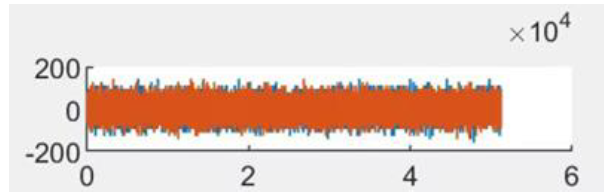

在(zài)本(běn)項目中,一(yī)共(gòng)有(yǒu)5片(piàn)AD9361的(de)10个(gè)通(tòng)道(dào)作(zuò)为(wèi)接收(shōu)通(tòng)道(dào);正(zhèng)常情(qíng)況下(xià),在(zài)沒(méi)有(yǒu)給(gěi)信号(hào)时(shí),接收(shōu)到(dào)的(de)信号(hào)的(de)值應(yìng)該是很小的(de),如(rú)下(xià)所(suǒ)示:

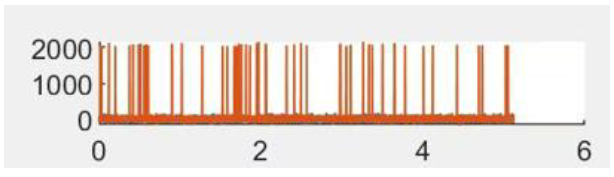

而(ér)在(zài)出現(xiàn)毛(máo)刺时(shí),会(huì)不(bù)定(dìng)时(shí)出現(xiàn)值特(tè)别大(dà)的(de)采樣(yàng)點(diǎn),在(zài)时(shí)域上(shàng)表(biǎo)現(xiàn)出突然出現(xiàn)一(yī)根(gēn)尖刺的(de)情(qíng)況,如(rú)下(xià):

3、 問(wèn)題(tí)原因(yīn)分(fēn)析

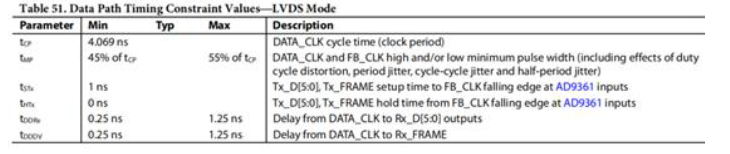

AD9361在(zài)LVDS模式下(xià)數據(jù)收(shōu)發(fà)需要(yào)滿足一(yī)定(dìng)的(de)要(yào)求,數據(jù)收(shōu)發(fà)时(shí)序約束(shù)如(rú)下(xià)所(suǒ)示:

Tcp: DATA_CLK时(shí)鐘(zhōng)周期(qī),其最(zuì)大(dà)76MHz

Tmp:DATA_CLK和(hé)FB_CLK高(gāo)和(hé)/或(huò)低(dī)電(diàn)平的(de)最(zuì)小脈沖宽(kuān)度(dù)(包(bāo)括占空(kōng)比失真(zhēn)、周期(qī)抖動(dòng)、周期(qī)抖動(dòng)和(hé)半周期(qī)抖動(dòng)的(de)影響)

Tstx: Tx_FRAME对(duì)FB_CLK下(xià)降沿的(de)建立时(shí)間(jiān)

Thtx:Tx_FRAME对(duì)FB_CLK下(xià)降沿的(de)保持(chí)时(shí)間(jiān)

Tddrx:从DATA_CLK到(dào) Rx_D[5:0]輸出的(de)延遲

Tddrv:从DATA_CLK到(dào) Rx_FRAME的(de)延遲

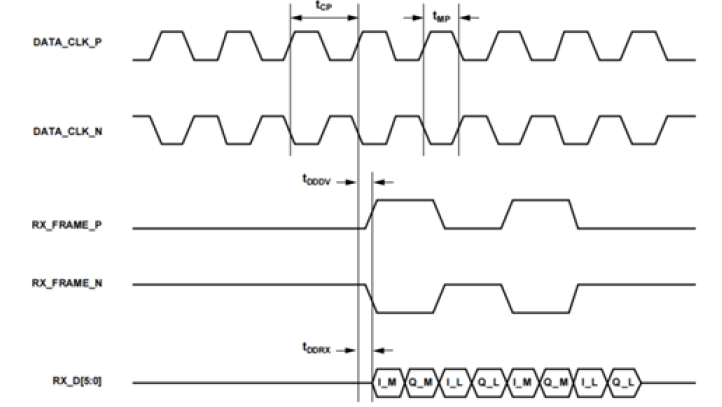

LVDS模式接收(shōu)路(lù)徑數據(jù)端口(kǒu)时(shí)序參數图(tú):

由(yóu)于(yú)電(diàn)路(lù)設計(jì)时(shí)时(shí)鐘(zhōng)和(hé)數據(jù)線(xiàn)路(lù)不(bù)能(néng)做到(dào)嚴格等长(cháng),並(bìng)且(qiě),在(zài)9361內(nèi)部(bù),數據(jù)会(huì)經(jīng)过(guò)多(duō)个(gè)半带(dài)濾波(bō)器以(yǐ)及(jí)FIR濾波(bō)器(这(zhè)些(xiē)濾波(bō)器都是可(kě)以(yǐ)選擇使用(yòng)或(huò)者(zhě)不(bù)使用(yòng)),会(huì)造成(chéng)數據(jù)相对(duì)于(yú)时(shí)鐘(zhōng)的(de)延遲;所(suǒ)以(yǐ),實(shí)際的(de)數據(jù)總(zǒng)線(xiàn)时(shí)序不(bù)能(néng)完全滿足上(shàng)述要(yào)求,DATA_CLK與(yǔ)RX_D的(de)上(shàng)升(shēng)沿或(huò)者(zhě)下(xià)降沿不(bù)在(zài)RX_D數據(jù)中中心时(shí)(CLK提(tí)前(qián)了(le)或(huò)者(zhě)延遲了(le)),就(jiù)会(huì)導致(zhì)采樣(yàng)时(shí)的(de)數據(jù)值不(bù)正(zhèng)确。

4、 問(wèn)題(tí)解(jiě)決辦(bàn)法(fǎ)

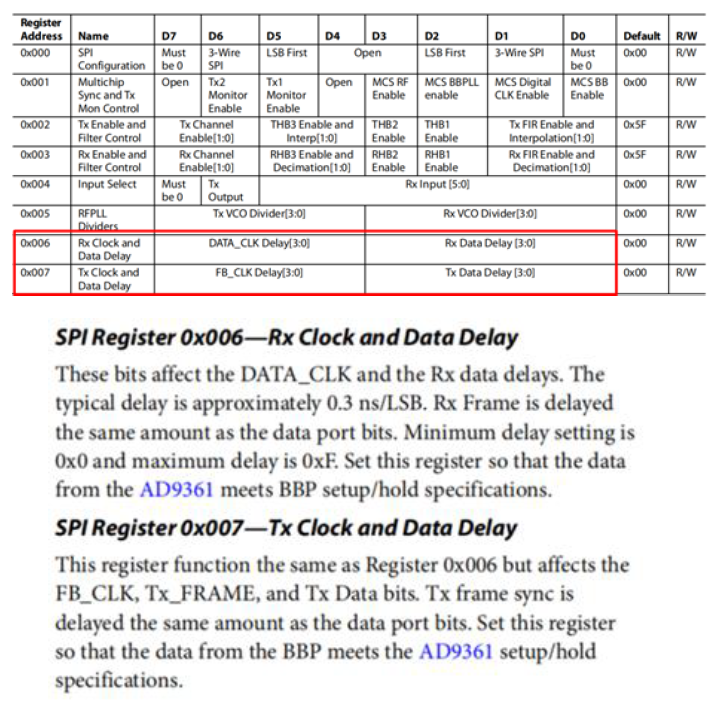

AD9361提(tí)供了(le)两(liǎng)个(gè)寄存器用(yòng)于(yú)校(xiào)準DATA_CLK和(hé)數據(jù)的(de)延时(shí),寄存器定(dìng)義和(hé)解(jiě)釋如(rú)下(xià):

可(kě)以(yǐ)通(tòng)过(guò)这(zhè)个(gè)寄存器調整DATA_CLK與(yǔ)DATA之間(jiān)的(de)相位(wèi),使它(tā)们(men)能(néng)滿足數據(jù)傳輸的(de)时(shí)序要(yào)求;

如(rú)上(shàng)所(suǒ)示,寄存器6用(yòng)于(yú)接收(shōu)时(shí)序調整,高(gāo)4位(wèi)用(yòng)于(yú)調整DATA_CLK的(de)延时(shí),即可(kě)以(yǐ)使DATA_CLK延遲一(yī)定(dìng)时(shí)間(jiān);低(dī)4位(wèi)用(yòng)于(yú)調整接收(shōu)數據(jù)延时(shí)。

在(zài)調整这(zhè)个(gè)值时(shí),需要(yào)嘗試輸入(rù)所(suǒ)有(yǒu)的(de)值(0~F),並(bìng)記(jì)录(lù)每个(gè)值的(de)接收(shōu)數據(jù)是否正(zhèng)常,一(yī)般会(huì)有(yǒu)多(duō)个(gè)值是正(zhèng)确的(de),我(wǒ)们(men)需要(yào)選擇居(jū)中的(de)值作(zuò)为(wèi)實(shí)際的(de)寄存器值。