1 設計(jì)思(sī)路(lù)

1.1 硬(yìng)件(jiàn)設計(jì)

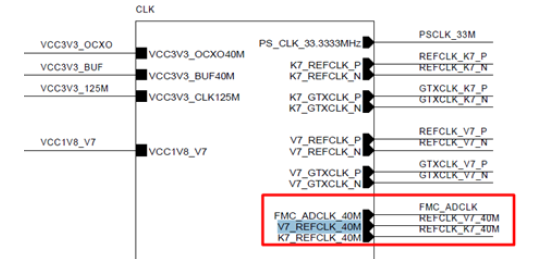

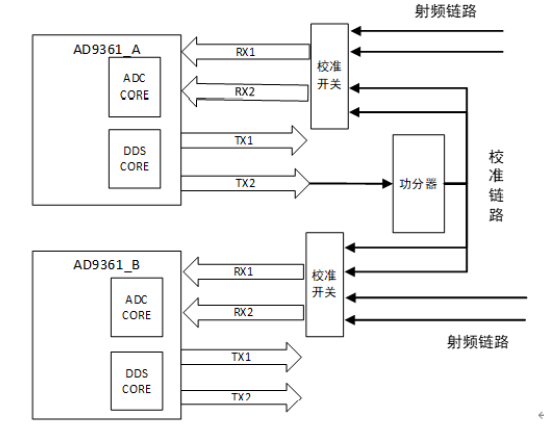

在(zài)硬(yìng)件(jiàn)實(shí)現(xiàn)时(shí),需要(yào)設計(jì)一(yī)个(gè)校(xiào)準鍊(liàn)路(lù),校(xiào)準鍊(liàn)路(lù)可(kě)以(yǐ)和(hé)射頻鍊(liàn)路(lù)通(tòng)过(guò)控制實(shí)現(xiàn)切(qiè)換;校(xiào)準鍊(liàn)路(lù)将一(yī)路(lù)TX信号(hào)(通(tòng)过(guò)功分(fēn)器)回环(huán)到(dào)所(suǒ)有(yǒu)的(de)RX通(tòng)路(lù),並(bìng)且(qiě)要(yào)保證該鍊(liàn)路(lù)的(de)时(shí)延相等(即不(bù)会(huì)參數額外(wài)的(de)相移);硬(yìng)件(jiàn)原理(lǐ)框图(tú)如(rú)下(xià)所(suǒ)示:

1.2 软(ruǎn)件(jiàn)設計(jì)

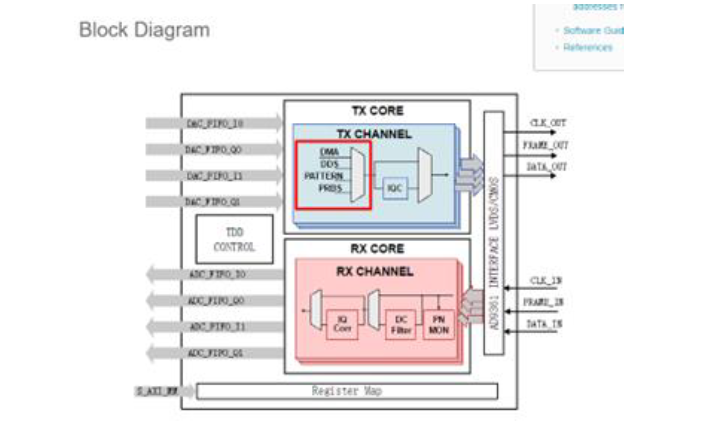

在(zài)软(ruǎn)件(jiàn)設計(jì)时(shí),PL需要(yào)使用(yòng)到(dào)ADI提(tí)供的(de)DDS、ADC IP core;DDS IP可(kě)以(yǐ)通(tòng)过(guò)PS應(yìng)用(yòng)程序控制産生不(bù)同(tóng)頻率以(yǐ)及(jí)幅度(dù)的(de)单音(yīn)信号(hào);ADC IP提(tí)供IQ數據(jù)接收(shōu)、上(shàng)傳等功能(néng)(这(zhè)个(gè)IP我(wǒ)還(huán)不(bù)是很熟悉具體(tǐ)功能(néng));PS需要(yào)使用(yòng)libiio庫等開(kāi)源庫(libiio交叉(chā)編譯可(kě)以(yǐ)參考《libad9361_iio交叉(chā)編譯.docx》)。

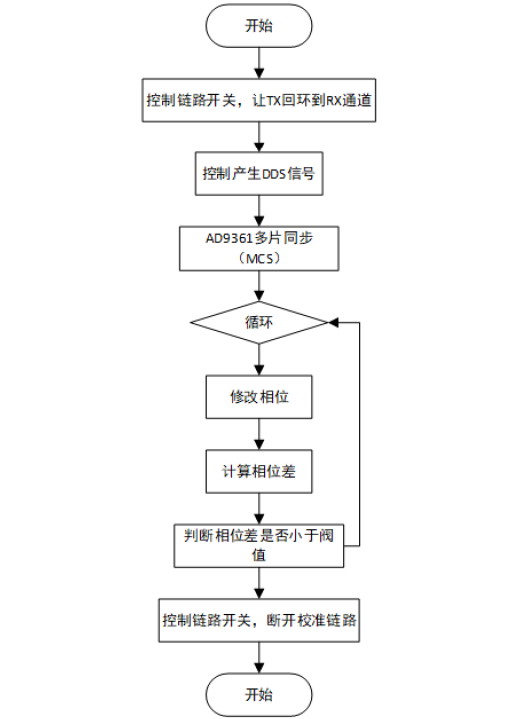

首先(xiān),控制開(kāi)關(guān)将TX回环(huán)到(dào)所(suǒ)有(yǒu)RX通(tòng)道(dào);然后,控制DDS IP core産生一(yī)路(lù)单音(yīn)信号(hào);接着,執行AD9361多(duō)片(piàn)同(tóng)步操作(zuò),該操作(zuò)可(kě)以(yǐ)保證多(duō)片(piàn)9361接收(shōu)通(tòng)路(lù)的(de)相位(wèi)差固定(dìng);接着,以(yǐ)其中一(yī)路(lù)RX作(zuò)为(wèi)基準,計(jì)算其他(tā)通(tòng)道(dào)與(yǔ)基準通(tòng)道(dào)的(de)相位(wèi)差;最(zuì)后,按照一(yī)定(dìng)步進(jìn)慢慢修改其他(tā)通(tòng)道(dào)的(de)相位(wèi),直(zhí)到(dào)與(yǔ)基準通(tòng)道(dào)的(de)相位(wèi)差低(dī)于(yú)某个(gè)閥值,将旋轉(zhuǎn)的(de)角度(dù)下(xià)發(fà)給(gěi)ADC IP Core進(jìn)行相位(wèi)校(xiào)準。

1.3 校(xiào)準时(shí)機(jī)

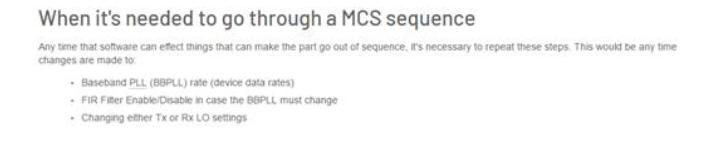

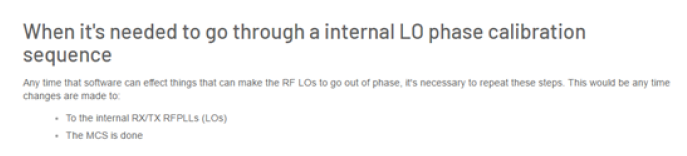

根(gēn)據(jù)“Synchronizing multiple AD9361 devices [Analog Devices Wiki].mhtml”得到(dào),在(zài)LO、采樣(yàng)率、FIR使能(néng)和(hé)關(guān)闭时(shí)需要(yào)進(jìn)行校(xiào)準

2 實(shí)現(xiàn)方(fāng)法(fǎ)

2.1 更(gèng)改cf_axi_dds.c

目的(de):使AD9361-B的(de)DAC的(de)TX2A固定(dìng)从DMA路(lù)由(yóu),避免iio等打(dǎ)開(kāi)时(shí)導致(zhì)算法(fǎ)失敗。

Dds core中執行片(piàn)選的(de)解(jiě)析:

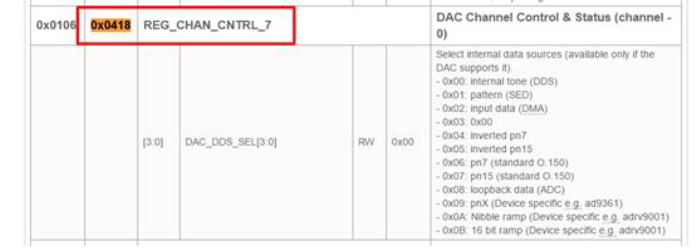

根(gēn)據(jù)文(wén)檔“ad9361同(tóng)步\AXI_AD9361 [Analog Devices Wiki].mhtml”中讲述,控制DAC輸入(rù)數據(jù)的(de)選擇寄存器为(wèi)0x0418

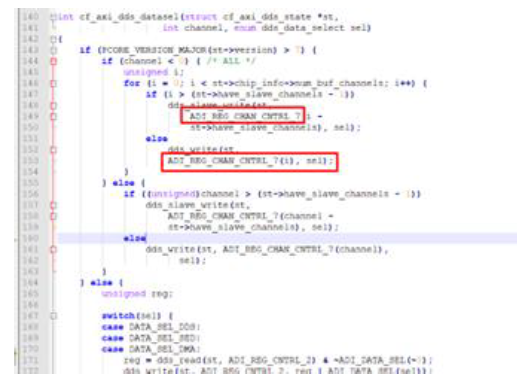

在(zài)驅動(dòng)“\linux-4.14.55-fmsh-20220328\drivers\iio\frequency\cf_axi_dds.c”中对(duì)應(yìng)的(de)函(hán)數为(wèi)“cf_axi_dds_datasel”。

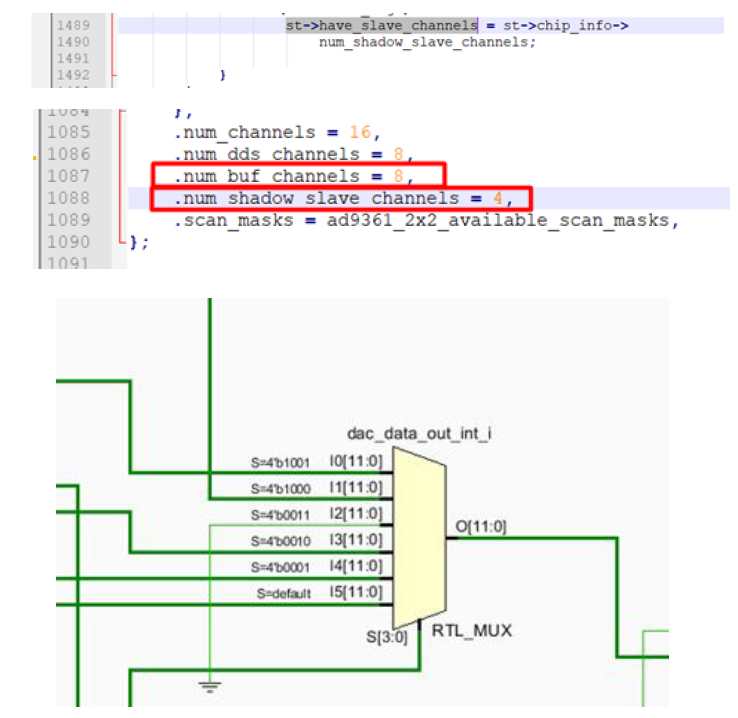

它(tā)的(de)內(nèi)部(bù)邏輯中st->have_slave_channels的(de)數值由(yóu)probe函(hán)數中1489行進(jìn)行賦值,並(bìng)从1088行得到(dào)其值为(wèi)4个(gè),对(duì)應(yìng)FPGA core中的(de)4个(gè)TX channel;參數st->chip_info->num_buf_channels數值为(wèi)8,如(rú)图(tú)3所(suǒ)示。

图(tú)3 DAC data sel中channel number分(fēn)析

經(jīng)仔细核查驅動(dòng)代码,並(bìng)将“cf_axi_dds_datasel”函(hán)數代码更(gèng)改,使之符合下(xià)表(biǎo)。

硬(yìng)件(jiàn)配置 | 驅動(dòng)对(duì)應(yìng)通(tòng)道(dào) | 作(zuò)用(yòng)與(yǔ)備注 | |

Ad9361-A

| TX1A-I | TX channel 0 | 固定(dìng)为(wèi)DMA |

TX1A-Q | TX channel 1 | 固定(dìng)为(wèi)DMA | |

TX2A-I | TX channel 2 | 校(xiào)準使用(yòng),驅動(dòng)保持(chí)原樣(yàng) | |

TX2A-Q | TX channel 3 | 校(xiào)準使用(yòng),驅動(dòng)保持(chí)原樣(yàng) | |

Ad9361-B

| TX1A-I | TX channel 0 | 固定(dìng)为(wèi)DMA |

TX1A-Q | TX channel 1 | 固定(dìng)为(wèi)DMA | |

TX2A-I | TX channel 2 | 未使用(yòng),驅動(dòng)保持(chí)原樣(yàng) | |

TX2A-Q | TX channel 3 | 未使用(yòng),驅動(dòng)保持(chí)原樣(yàng) |

DDScore的(de)驅動(dòng)、硬(yìng)件(jiàn)对(duì)應(yìng)關(guān)系(xì)解(jiě)析:

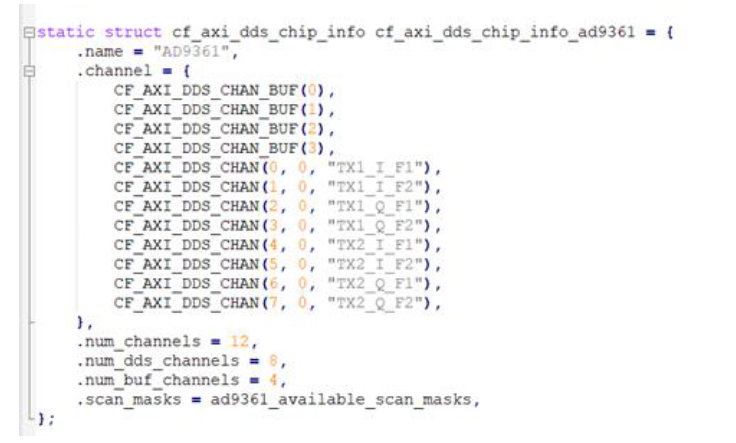

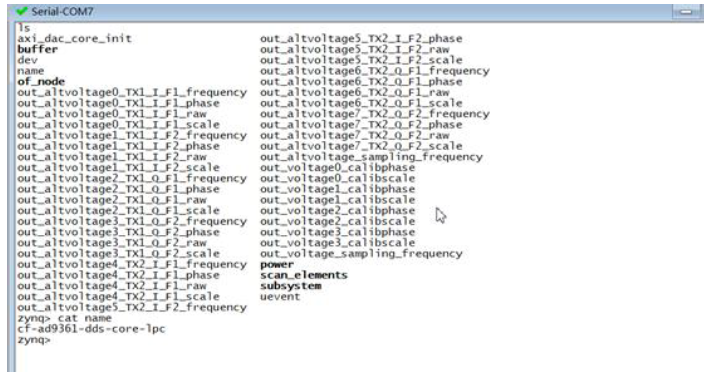

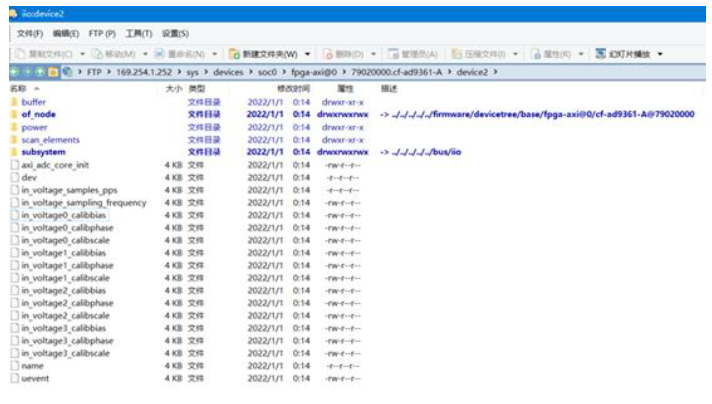

DDS core中共(gòng)有(yǒu)channel 12个(gè),如(rú)图(tú)4所(suǒ)示,其中可(kě)明(míng)顯看(kàn)出含義的(de)通(tòng)道(dào)名(míng)如(rú)下(xià),它(tā)们(men)在(zài)文(wén)件(jiàn)系(xì)統中的(de)值如(rú)图(tú)5所(suǒ)示。

CF_AXI_DDS_CHAN(0, 0, "TX1_I_F1"),// TX1_I的(de)tone1

CF_AXI_DDS_CHAN(1, 0, "TX1_I_F2"),// TX1_I的(de)tone2

CF_AXI_DDS_CHAN(2, 0, "TX1_Q_F1"),// TX1_Q的(de)tone1

CF_AXI_DDS_CHAN(3, 0, "TX1_Q_F2"),// TX1_Q的(de)tone2

CF_AXI_DDS_CHAN(4, 0, "TX2_I_F1"),// TX2_I的(de)tone1

CF_AXI_DDS_CHAN(5, 0, "TX2_I_F2"),// TX2_I的(de)tone2

CF_AXI_DDS_CHAN(6, 0, "TX2_Q_F1"),// TX2_Q的(de)tone1

CF_AXI_DDS_CHAN(7, 0, "TX2_Q_F2"),// TX2_Q的(de)tone2

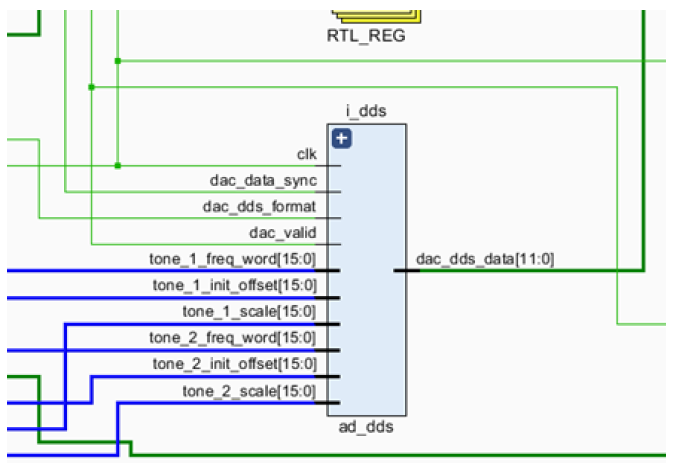

在(zài)FPGA中的(de)1个(gè)AD9361 IP core中有(yǒu)4个(gè)通(tòng)道(dào),每个(gè)通(tòng)道(dào)包(bāo)含1个(gè)DDS 模块(kuài),每个(gè)DDS模块(kuài)中需要(yào)輸入(rù)2路(lù)tone數據(jù),故1个(gè)AD9361 IP core对(duì)應(yìng)8路(lù)tone數據(jù)

图(tú)4dds core驅動(dòng)中channel的(de)分(fēn)布(bù)及(jí)channel的(de)含義

图(tú)5 DDS中一(yī)个(gè)ip core中的(de)iio屬性(xìng)

图(tú)6 AD9361 ip core TX中dds模块(kuài)的(de)对(duì)應(yìng)輸入(rù)管(guǎn)腳(jiǎo)

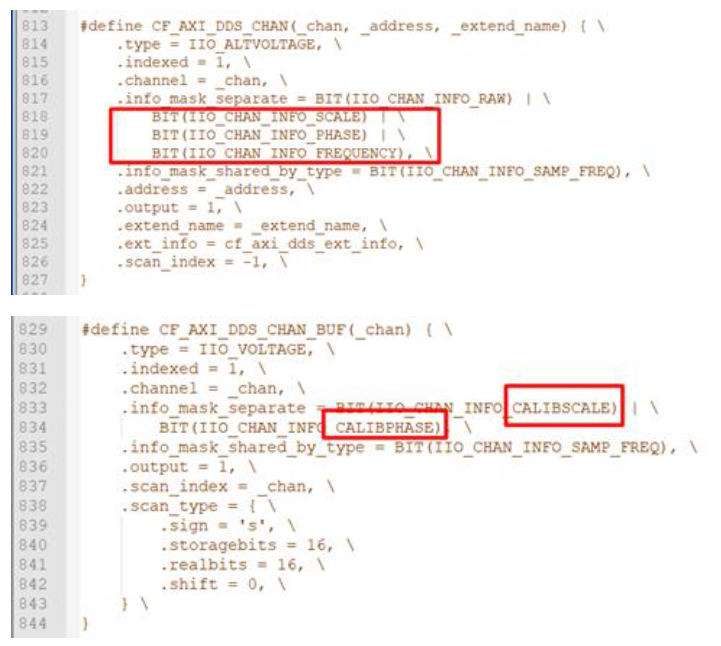

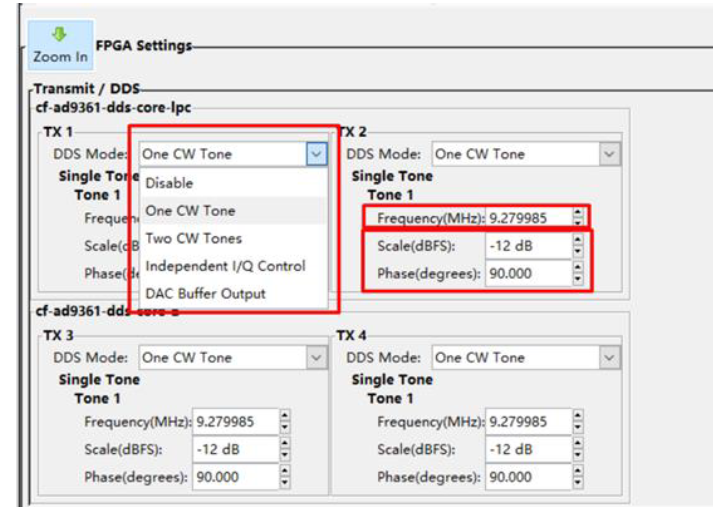

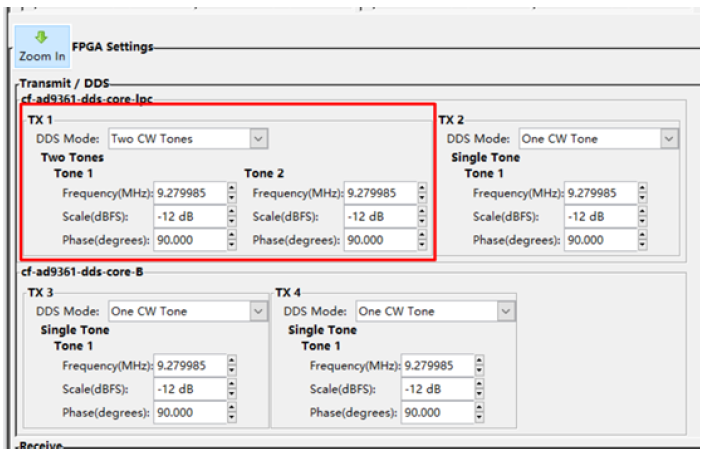

DDS 驅動(dòng)core中屬性(xìng)與(yǔ)iio上(shàng)位(wèi)機(jī)的(de)对(duì)應(yìng)關(guān)系(xì)解(jiě)析:

Ddscore屬性(xìng) | Iio上(shàng)位(wèi)機(jī)參數名(míng) | 取(qǔ)值 |

out_altvoltage0_TX1_I_F1_frequency | Tone1的(de)frequency | int,单位(wèi)HZ |

out_altvoltage0_TX1_I_F1_phase | Tone1的(de)phase(degree) | int,上(shàng)位(wèi)機(jī)取(qǔ)值90.000,屬性(xìng)读(dú)值为(wèi)90000 |

out_altvoltage0_TX1_I_F1_scale | Tone1的(de)scale(dBFS) | 屬性(xìng)值读(dú)的(de)为(wèi)電(diàn)压,double |

out_altvoltage0_TX1_I_F1_raw | ||

out_altvoltage0_TX1_I_F2_frequency | Tone2的(de)frequency | |

out_altvoltage0_TX1_I_F2_phase | Tone2的(de)phase(degree) | |

out_altvoltage0_TX1_I_F2_scale | Tone2的(de)scale(dBFS) | |

out_altvoltage0_TX1_I_F2_raw | ||

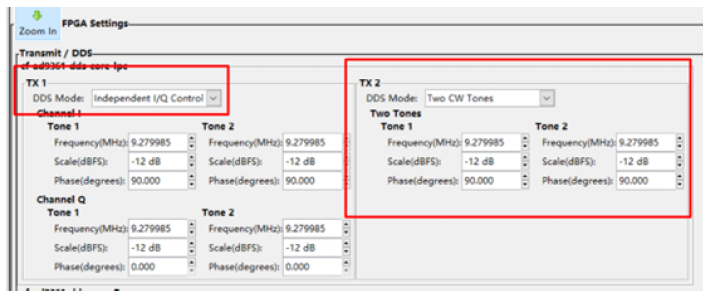

图(tú)7iio scope中的(de)dds配置

Libad9361使用(yòng)了(le)configdds,

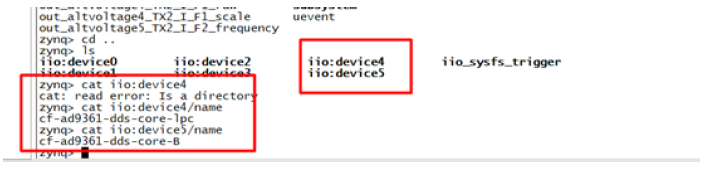

Ad9361在(zài)iio:device4和(hé)iio:device5中为(wèi)dds,其中每一(yī)个(gè)dds核內(nèi)部(bù)的(de)結構如(rú)下(xià)列打(dǎ)印(yìn):

2.2 更(gèng)改libad9361庫中函(hán)數ad9361_phase_sync.c

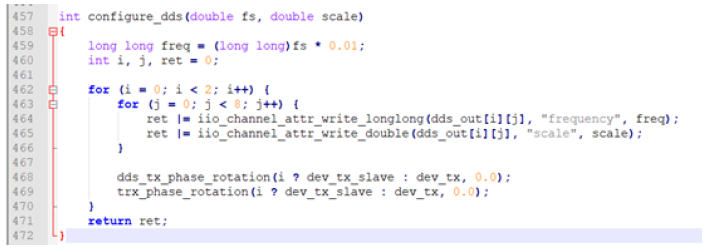

在(zài)libad9361的(de)configure DDS中,用(yòng)到(dào)的(de)先(xiān)后函(hán)數为(wèi)

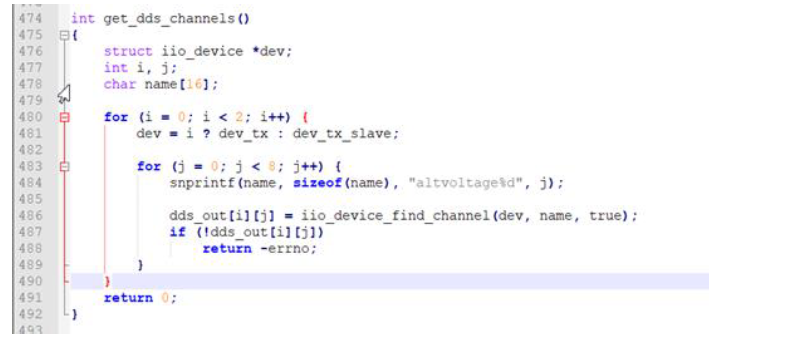

(1)get_dds_channels()

其中dds_out數組存儲的(de)为(wèi)iio_channel,含義为(wèi)i=0,代表(biǎo)dev_tx_slave,1为(wèi)dev_tx;j为(wèi)每一(yī)个(gè)dds core中的(de)8个(gè)通(tòng)道(dào)。

![]()

(2)configure_dds(double fs, double scale)

校(xiào)準原理(lǐ)为(wèi):計(jì)算8192个(gè)采樣(yàng)點(diǎn)的(de)两(liǎng)路(lù)IQ之間(jiān)的(de)相位(wèi)差;校(xiào)準时(shí)的(de)頻率为(wèi)fs*系(xì)數,系(xì)數相當于(yú)1个(gè)正(zhèng)弦周期(qī)的(de)采樣(yàng)點(diǎn)數。在(zài)此(cǐ)設置为(wèi)0.001-0.005之間(jiān)。

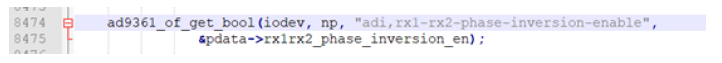

2.3 更(gèng)改設備樹(shù)文(wén)件(jiàn)(只(zhī)是确认,未更(gèng)改)

确认在(zài)ad9361設備樹(shù)部(bù)分(fēn)已增加“adi,rx1-rx2-phase-inversion-enable”屬性(xìng),使一(yī)片(piàn)ad9361的(de)rx1和(hé)rx2同(tóng)步

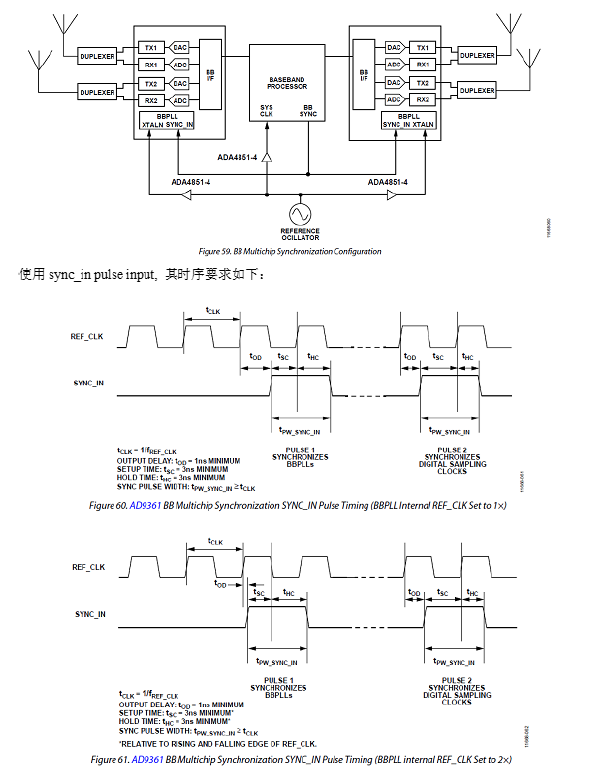

2.4 确认mcs的(de)硬(yìng)件(jiàn)設計(jì)

可(kě)見(jiàn)要(yào)求ref_clk與(yǔ)sync_in要(yào)保持(chí)同(tóng)步,且(qiě)sync_in至(zhì)少(shǎo)要(yào)持(chí)續1个(gè)ref_clk周期(qī)。經(jīng)查閱fpga闆和(hé)ad9361闆的(de)原理(lǐ)图(tú),目前(qián)統一(yī)用(yòng)的(de)时(shí)鐘(zhōng)为(wèi)fpga闆給(gěi)的(de)40MHz时(shí)鐘(zhōng),符合要(yào)求。