在(zài)工程設計(jì)中,有(yǒu)源器件(jiàn)的(de)饋電(diàn)端都有(yǒu)对(duì)地(dì)的(de)濾波(bō)電(diàn)容,尤其是模拟芯片(piàn),電(diàn)源饋電(diàn)端有(yǒu)好(hǎo)幾(jǐ)个(gè)電(diàn)容,容值呈階(jiē)梯(tī)变化(huà)。为(wèi)什(shén)麼(me)工程中要(yào)这(zhè)樣(yàng)設計(jì)呢?

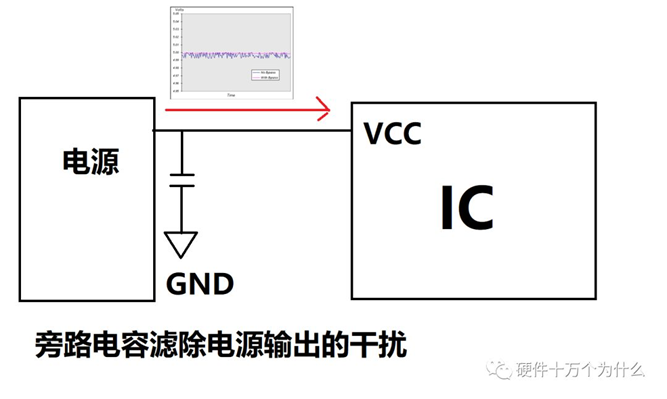

電(diàn)源輸出端的(de)对(duì)地(dì)電(diàn)容为(wèi)旁路(lù)電(diàn)容,主(zhǔ)要(yào)作(zuò)用(yòng)是在(zài)電(diàn)源輸出端與(yǔ)GND直(zhí)接建立一(yī)个(gè)高(gāo)頻旁路(lù)通(tòng)道(dào),降低(dī)高(gāo)頻噪聲。如(rú)下(xià)图(tú)所(suǒ)示。

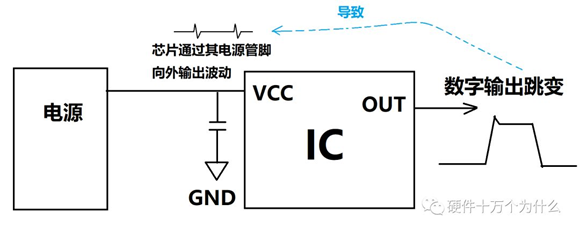

負载器件(jiàn)的(de)饋電(diàn)端对(duì)地(dì)電(diàn)容为(wèi)去(qù)耦電(diàn)容,作(zuò)用(yòng)是抑制器件(jiàn)工作(zuò)造成(chéng)饋電(diàn)端口(kǒu)的(de)波(bō)動(dòng)。如(rú)下(xià)图(tú)所(suǒ)示。

在(zài)濾波(bō)電(diàn)容設計(jì)中,我(wǒ)们(men)更(gèng)希望的(de)是濾波(bō)電(diàn)容对(duì)地(dì)的(de)高(gāo)頻阻抗盡量(liàng)小,才能(néng)达(dá)到(dào)更(gèng)好(hǎo)的(de)濾波(bō)效果(guǒ)。

二(èr)、電(diàn)容等效模型

理(lǐ)想(xiǎng)電(diàn)容的(de)阻抗为(wèi):Xc = 1/jwC

其中w为(wèi)角頻率,w = 2πf。

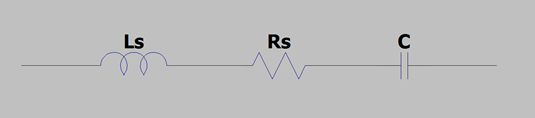

而(ér)實(shí)際電(diàn)容等效模型如(rú)下(xià):

等效阻抗为(wèi):

Xc = Rs + jwL + 1/jwC

= Rs + j(wL-1/wC)

當wL-1/wC=0时(shí),即w=1/√LC时(shí),電(diàn)容阻抗最(zuì)小,等于(yú)Rs,此(cǐ)时(shí)的(de)頻率f=w/2π为(wèi)電(diàn)容的(de)自(zì)諧振頻率;

當wL-1/wC<0时(shí),電(diàn)容呈容性(xìng);

當wL-1/wC>0时(shí),電(diàn)容呈感(gǎn)性(xìng)。

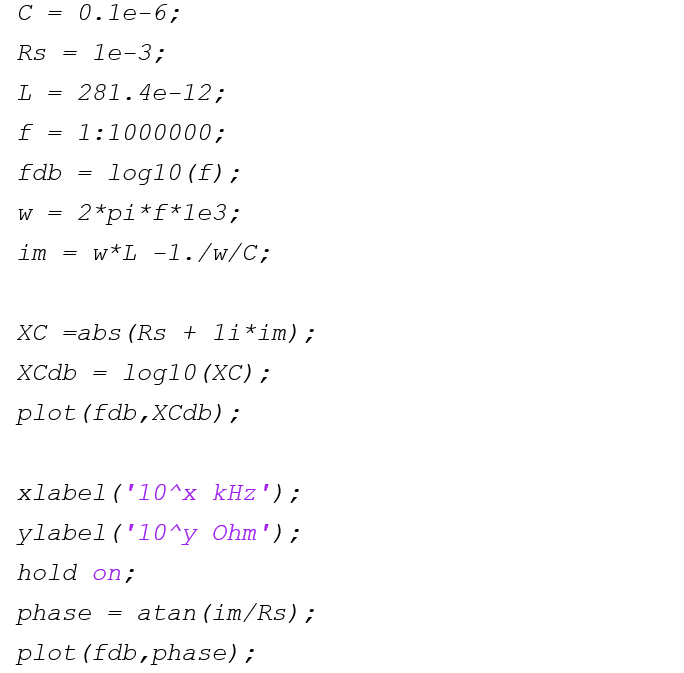

以(yǐ)一(yī)个(gè)容值为(wèi)0.1uF,等效電(diàn)阻为(wèi)1mΩ,電(diàn)感(gǎn)值为(wèi)281.4pH的(de)電(diàn)容为(wèi)例,仿真(zhēn)其在(zài)1kHz到(dào)1000MHz範圍內(nèi)的(de)阻抗变化(huà),matlab代码如(rú)下(xià):

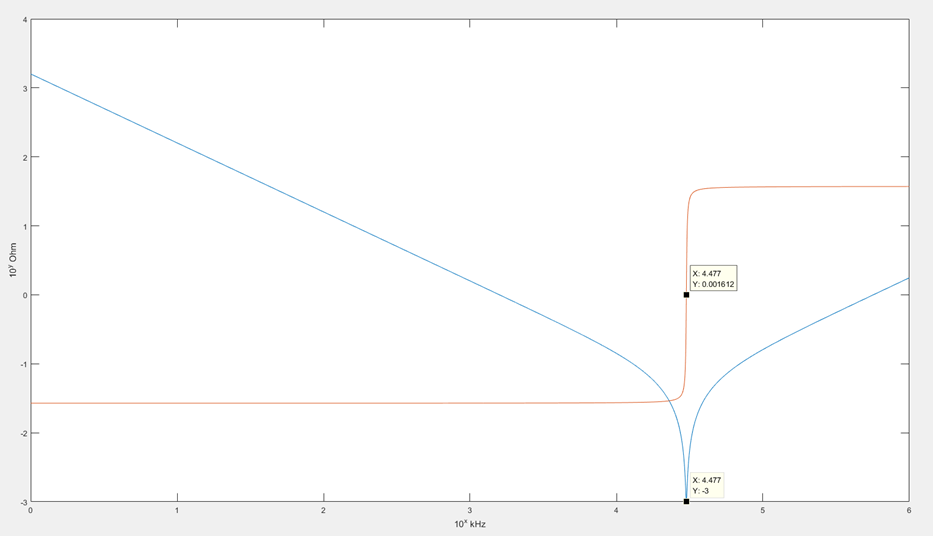

可(kě)以(yǐ)看(kàn)出,電(diàn)容在(zài)104.477kHz(約30MHz)时(shí)諧振,阻抗最(zuì)小,为(wèi)Rs = 1mΩ,當頻率小于(yú)諧振頻率时(shí),電(diàn)容呈容性(xìng),當頻率大(dà)于(yú)諧振頻率时(shí),電(diàn)容呈感(gǎn)性(xìng)。